US $124.00

| Condition: |

New: A brand-new, unused, unopened, undamaged item in its original packaging (where packaging is

applicable). Packaging should be the same as what is found in a retail store, unless the item is handmade or was packaged by the manufacturer in non-retail packaging, such as an unprinted box or plastic bag. See the seller's listing for full details.

...

|

Brand | NXP |

| MPN | LPC1768FBD100 | ||

| Model | GoJGo.com-10155 | ||

| IC Package | LQFP100_14X14X05P |

Directions

Similar products from Electrical Integrated Circuits & Processors

MM58167AN Real Time Clock Calendar National Semiconduct

1 Piece New Ralink RTS390RL RT539ORL RTS39ORL RT5390RL QFN56 IC Chip

1pcs Red 2.54mm Pitch 8 pins 4 Positions Ways Slide Type DIP Switch

10pcs 6X6X5mm Tact Switches 4 Legs high quanlity

Rockwell- A4002 15472PA 42-Pin Staggered DIL- Very Rare

Rockwell R6645-20 Data Control Chip, Serial Com Ports

800 PCS VISHAY 16CTQ1005TRLPBF

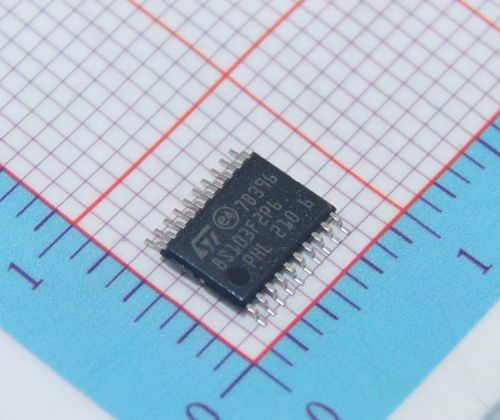

100 pcs/lot IC STM8S103F2P6, 16 MHz STM8S 8-bit MCU, up to 8 Kbytes Flash

Waterproof Digital Thermal Probe or Sensor DS18B20

100 pcs/lot IC STM8S207C8T6, 24 MHz STM8S 8-bit MCU, up to 128 KB Flash

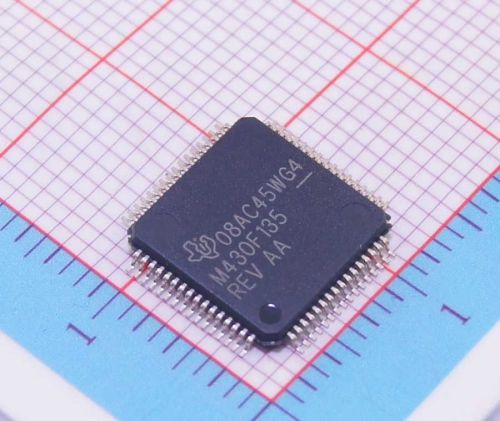

25 pcs/lot IC MSP430F135IPMR,Texas Instruments MSP430 family of MCU

45 EPROM Memory & IC Integrated Circuit Chips, Used / Previously Owned

K4D261638K-LC40 SAMSUNG 32A330 SERIES

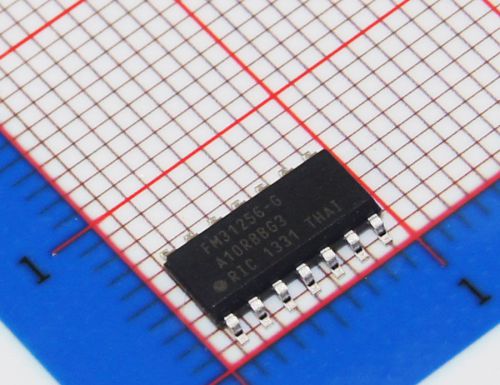

10 pcs FM31256-GTR, Integrated Processor Companion with Memory

50 pcs IMP812LEUS-T, 4-Pin ?P Voltage Supervisor with Manual Reset

10pcs 78L08 100mA 8V TO-92 Voltage Regulator Positive

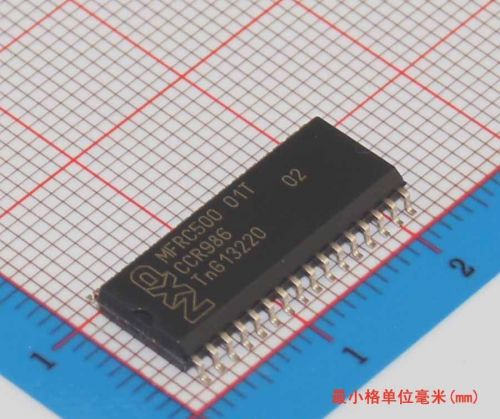

25 pcs/lot IC MFRC500, Highly Integrated ISO/IEC 14443 A Reader IC

ICS ICS85304AG-01LF Low Skew, 1-to-5, Differential-to-3.3V LVPECL Fanout Buffer

25 pcs/lot STM32F105RBT6, ARM-based 32-bit MCU with 64/256 KB Flash

Vintage AMD 1404A AM1404A 1024-BIT Shift Register Memory board GE

People who viewed this item also vieved

STRONG MAGNET LED LAMP INDUSTRIAL MACHINE AGE GOOSENECK LAMP PLUG IN SWITCH ON

Plastic Electronic Components Box Laboratory Storage cover 50P white chip saved

PHOTON X ELECTRONIC BALLAST T5HO

Pair Cunningham CX-301-A Amplifier Tubes, Good Condition, For Display Only

Sylvania 6L6GB black ribbed plate top D get made in USA tested very strong

WJ20X10116 GE Fan Mtr Capacitor Genuine OEM WJ20X10116

1500 PCS ROEDERSTEIN MKP1837-339/011-21 CAPACITORS

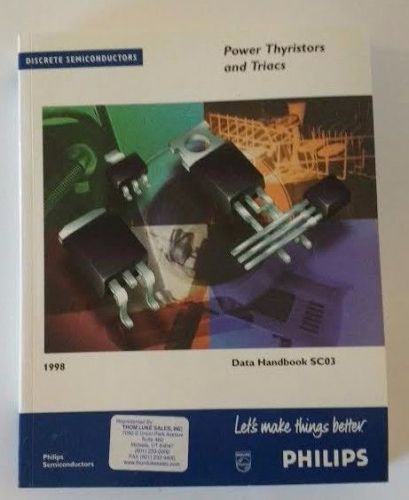

Philips Power Thyristors and Triacs 1998 Data Handbook Paperback

Siemens Discrete and RF Semiconductors Data Book 1998 Paperback

Lot of Five: 24 Pin IC Socket Pin Through Hole Solder DIP High Profile Wide Type

5V USBHUB USB2.0 Hub Concentrator 4-Female Precise USB Expansion Module

ASC battery charge regulator for photovoltaic systems ASC 24/16 SHIPS FREE!!!!!!

NEWEST DC-DC Step-Down Power Module Adjustable 3A V/I LCD Display with Case

By clicking "Accept All Cookies", you agree to the storing of cookies on your device to enhance site navigation, analyze site usage, and assist in our marketing efforts.

Accept All Cookies